Memòria a atzessu casuale

Sa memòria a atzessu casuale (connota comente RAM, acrònimu de s'inglesu Random Access Memory, in contrapositzione cun sa memòria a atzessu secuentziale), est unu tipu de memòria volàtile caraterizada dae su permìtere s'atzessu diretu a cale si siat indiritzu de memòria cun su matessi tempus de atzessu.

Funtzionamentu

[modìfica | modìfica su còdighe de orìgine]In sa memòria RAM sunt copiados (carrigados) is programmas chi su protzessore depet esecutare e is datos chi custos depent impreare. Una borta chi su programma est serradu, sas mudas fatas, si no sunt sarvadas in su discu tèteru o subra àtera memòria non volàtile, ant a èssere pèrdidas.

Pro sas caraterìsticas suas, sa RAM est impreada comente a memòria primària in is elaboradores prus comunos.

Su tipu de memòria a atzessu casuale prus comunu, oe in die, est a istadu sòlidu, a letura-iscritura e volàtile, ma sunt memòrias a atzessu casuale sa majoria de is tipos de ROM (memòria a sola letura), sa NOR Flash (unu tipu de memòria flash) e vàrios tipos de memòrias informàticas impreadas a su printzìpiu de s'informàtica e oe non prus impreadas, comente sa memòria a nùcleu magnèticu.

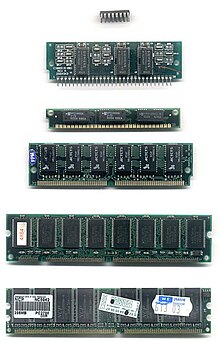

S'acrònimu RAM (non su tèrmine "memòria a atzessu casuale") tenet fintzas unu segundu sentidu prus restrintu, ma oe in die prus difùndidu, chi identìficat sas ischedas fìsicas chi benint installadas in is elaboradores de oe (bide mòdulos DIMM, SIMM, SO-DIMM).

Su tzircùitu chi permitit de ammentare unu bit de datos ddi narant tzella. In antis de pòdere iscrìere o lèghere datos in sa memòria, unu grupu de tzellas depet èssere isseberadu. Custu benet fatu aplichende signales elètricos a unas cantas lìnias de indiritzu. Unu grupu de tzircùitos multiplexer e demultiuplexer sunt impreados pro ativare is tzellas chi currispondent a s'indiritzu isseberadu.

Tipologias

[modìfica | modìfica su còdighe de orìgine]

In sa SRAM, acrònimu de Static Random Access Memory (RAM istàtica) ogni bit est costituidu dae unu Flip-Flop de tipu D.

Cunsentint de mantènnere sas informatziones pro unu tempus infinitu, sunt meda lestras e consumant pagu energia. Sa netzessidade de impreare medas cumponentes, però, ddas faghet gastosas, prus mannas e cun un'iscassa càbida.

Pro is caraterìsticas issoro, sunt a parusu impreadas pro is memòrias cache.[1]

In sa DRAM, acrònimu de Dynamic Random Access Memory (RAM dinàmica), ogni bit est costituidu dae unu transistor e chi separat unu cundensadore, chi mantenet s'informatzione.

Pro neghe de s'isulamentu non perfetu, su cundensadore si iscàrrigat, tando a pustis de pagu tempus su cuntentu suo bessit inaffidabile. Est netzessàriu duncas a ddu torrare a carrigare in antis chi custu acontessat. Custa operatzione est narada "refriscamentu" (refreshing). Custa operatzione est esecutada dae unu tzircùitu internu a sa memòria etotu. Custu rechedet unu gastu de energia prus mannu e faghet sa memòria prus lenta, ca mentras su refriscamentu est esecutende, no est possìbile a dda lèghere. Is memòrias sunt bastante fidadas, pro ite s'ispissu a ogni riga de sa memòria est assotziadu unu bit de paridade, chi cunsentit de individuare errores sìngulos a s'internu de sa riga, opuru una sèrie de bit, chi gènerant unu còdighe de Hamming, chi cunsentit de individuare e curregire errores sìngulos e individuare errores dòpios.

Pro ogni tzella ddoe at unu nùmeru bàsciu de cumponentes, isceti unu transistor imbetzes de is ses de sa SRAM chi permitent de otènnere una capatzidade arta de su dispositivu, una rechesta bassa de potèntzia e gastos reduidos. Sunt duncas impreadas s'ispissu pro sa memòria printzipale de su sistema.[2]

SDRAM

[modìfica | modìfica su còdighe de orìgine]

S'ispissu saldada in unu mòdulu de tipu DIMM, est a parusu impreada comente a memòria printzipale de sos Personal Computer de tipu Pentium e imbenientes.

Esèmpios:

- SDR SDRAM: indicat sas memòrias originàrias SDRAM. Cun s'evolutzione tècnica, custu tipu at pigadu su sufissu SDR, est a nàrrere Single Dada Rate, pro ddas diferentziare de sas SDRAM imbenientes cun controllore DDR. Su single dada rate indicaiat s'atzetamentu de unu cumandu e su trasferimentu de 1 faeddu de datos pro tziclu de relògiu (a parusu, 100 e 133 MHz).

- DDR SDRAM

- DDR2

- DDR3

- DDR4

- SODIMM: de notare chi su formatu SODIMM no cuntenet semper memòria SDRAM.

Impreos

[modìfica | modìfica su còdighe de orìgine]Gerarchia de memòria

[modìfica | modìfica su còdighe de orìgine]In medas sistemas informàticos sa memòria est organizada comente a gerarchia. Custa organizatzione est de importu mannu, ca podet fàghere una diferèntzia manna in is prestatzionis de su sistema.

Is bator livellos tìpicos sunt:[3]

- Internu - Registros de su protzessore e cache

- Primària - sa RAM de sistema

- Segundària - Memòria de massa (discos fissos e àteros dispositivos) in lìnea

- Memòrias esternas de massa

In custu modellu generale, sa memòria a atzessu casuale est impreada pro is primos duos livellos. Sa memòria primària est bèndida comente a mòdulos de dimensione reduida, fàtziles de montare in s'elaboradore e de cambiare, in casu de netzessidade.

Àteros impreos

[modìfica | modìfica su còdighe de orìgine]Discu RAM

[modìfica | modìfica su còdighe de orìgine]Unu discu RAM (o discu virtuale, connotu comente a RAM disk puru) est una portzione de RAM impreada comente chi esseret unu discu fissu, cun s'avantàgiu de tènnere prestatziones in letura e iscritura meda prus artas, cun tempos de atzessu prus lestros. Unu discu de custu tipu est volàtile: su cuntentu chi no est copiadu in unu suportu permanente est pèrdidu cando su sistema est istudadu. Podent serbire pro atividades diferentes, pro esempru pro sa creatzione de archìvios temporàneos o fintzas pro s'installatzione de unu sistema operativu.[4]

Frecuèntzias a cunfrontu

[modìfica | modìfica su còdighe de orìgine]Sa memòria iscàmbiat dados cun sos àteros cumponentes pro mèdiu de su bus, chi tenet una frecuèntzia operativa sua de base, a mùltiplos de 33 MHz, gasi comente sa memòria e su protzessore. Sos tres cumponentes andant sincronizados in unu mùltiplu de sa frecuèntzia de base de su bus. Sa frecuèntzia interna de relògiu de sa memòria diferit de sa frecuèntzia de su bus de E/I de su mòdulu, chi est sa de s'interfàtzia intra su mòdulu etotu e sa piastra base.

In sa tabella a suta est possìbile bìdere sas frecuèntzias operativas de is tipos vàrios de mòdulos de memòria; si faghet riferimentu a is istandard impreados dae sos produtores e non a cussos istandardizados dae su JEDEC isceti:

| Tzircùitu

integradu |

Mòdulu | Frecuèntzia | Voltàgiu | |

|---|---|---|---|---|

| Canale sìngulu | Canale dòpiu | |||

| SDR-66 | PC-66 | 66 MHz | - | 3.30 V |

| SDR-100 | PC-100 | 100 MHz | - | 3.30 V |

| SDR-133 | PC-133 | 133 MHz | - | 3.30 V |

DDR (2002)

[modìfica | modìfica su còdighe de orìgine]| Tzircùitu

integradu |

Mòdulu | Frecuèntzia | Voltàgiu | |

|---|---|---|---|---|

| Canale sìngulu | Canale dòpiu | |||

| DDR-200 | PC-1600 | 100 MHz | 200 MHz | 2.50 V |

| DDR-266 | PC-2100 | 133 MHz | 266 MHz | 2.50 V |

| DDR-333 | PC-2700 | 166 MHz | 333 MHz | 2.50 V |

| DDR-400 | PC-3200 | 200 MHz | 400 MHz | 2.50 V |

DDR2 (2004)

[modìfica | modìfica su còdighe de orìgine]| Tzircùitu

integradu |

Mòdulu | Frecuèntzia | Voltàgiu | |

|---|---|---|---|---|

| Canale sìngulu | Canale dòpiu | |||

| DDR2-400 | PC2-3200 | 200 MHz | 200 MHz | 1.80 V |

| DDR2-533 | PC2-4200 | 266 MHz | 266 MHz | 1.80 V |

| DDR2-667 | PC2-5300 | 333 MHz | 667 MHz | 1.80 V |

| DDR2-800 | PC2-6400 | 400 MHz | 800 MHz | 1.80 V |

| DDR2-1066 | PC2-8500 | 533 MHz | 1.066 MHz | 1.80 V |

DDR3 (2007)

[modìfica | modìfica su còdighe de orìgine]| Tzircùitu

integradu |

Mòdulu | Frecuèntzia | Voltàgiu | ||

|---|---|---|---|---|---|

| Canale sìngulu | Canale dòpiu | Bàsciu | |||

| DDR3-800 | PC3-6400 | 400 MHz | 800 MHz | 1.50 V | 1.35 V |

| DDR3-1066 | PC3-8500 | 533 MHz | 1.066 MHz | 1.50 V | 1.35 V |

| DDR3-1333 | PC3-10600 | 667 MHz | 1.333 MHz | 1.50 V | 1.35 V |

| DDR3-1600 | PC3-12800 | 800 MHz | 1.600 MHz | 1.50 V | 1.35 V |

| DDR3-1866 | PC3-14900 | 933 MHz | 1.866 MHz | 1.50 V | 1.35 V |

| DDR3-2000 | PC3-16000 | 1.000 MHz | 2.000 MHz | 1.50 V | - |

| DDR3-2133 | PC3-17000 | 1.066 MHz | 2.133 MHz | 1.50 V | - |

| DDR3-2400 | PC3-19200 | 1.200 MHz | 2.400 MHz | 1.50 V | - |

| DDR3-2666 | PC3-21300 | 1.333 MHz | 2.666 MHz | 1.50 V | - |

DDR4 (2018)

[modìfica | modìfica su còdighe de orìgine]| Tzircùitu

integradu |

Mòdulu | Frecuèntzia | Voltàgiu | ||

|---|---|---|---|---|---|

| Canale sìngulu | Canale dòpiu | Bàsciu | |||

| DDR4-1600 | PC4-12800 | 800 MHz | 1.600 MHz | 1.20 V | 1.05 V |

| DDR4-1866 | PC4-14900 | 933 MHz | 1.966 MHz | 1.20 V | 1.05 V |

| DDR4-2133 | PC4-17000 | 1.066 MHz | 2.133 MHz | 1.20 V | 1.05 V |

| DDR4-2400 | PC4-19200 | 1.200 MHz | 2.400 MHz | 1.20 V | 1.05 V |

| DDR4-2666 | PC4-21300 | 1.333 MHz | 2.666 MHz | 1.20 V | 1.05 V |

| DDR4-3000 | PC4-24000 | 1.500 MHz | 3.000 MHz | 1.20 V | - |

| DDR4-3200 | PC4-25600 | 1.600 MHz | 3.200 MHz | 1.20 V | - |

| DDR4-4266 | PC4-34100 | 2.133 MHz | 4.266 MHz | 1.20 V | - |

| DDR4-4800 | PC4-38400 | 2.400 MHz | 4.800 MHz | 1.20 V | - |

| DDR4-5332 | PC4-42656 | 2.666 MHz | 5.332 MHz | 1.20 V | - |

| DDR4-5600 | PC4-44800 | 2.800 MHz | 5.600 MHz | 1.20 v | - |

| DDR4-6000 | PC4-48000 | 3.000 MHz | 6.000 MHz | 1.20 V | - |

| DDR4-6400 | PC4-51200 | 3.200 MHz | 6.400 MHz | 1.20 V | - |

| DDR4-6932 | PC4-55456 | 3.466 MHz | 6.932 MHz | 1.20 V | - |

| DDR4-8266 | PC4-66128 | 4.133 MHz | 8.266 MHz | 1.20 V | - |

| DDR4-8532 | PC4-68256 | 4.266 MHz | 8.532 MHz | 1.20 V | - |

| DDR4-8666 | PC4-69328 | 4.333 MHz | 8.666 MHz | 1.20 V | - |

| DDR4-8800 | PC4-70400 | 4.400 MHz | 8.800 MHz | 1.20 V | - |

| DDR4-9000 | PC4-72000 | 4.500 MHz | 9.000 MHz | 1.20 V | - |

| DDR4-9200 | PC4-73000 | 4.600 MHz | 9.200 MHz | 1.20 V | - |

Notas

[modìfica | modìfica su còdighe de orìgine]- ↑ Tanenbaum, Andrew S. e Austin, Todd, Architettura dei calcolatori : un approccio strutturale, 6. ed, Pearson, 2013, p. 187, ISBN 9788871929620, OCLC 928913777. URL consultadu su 2 cabudanni 2019.

- ↑ Tanenbaum, Andrew S. e Austin, Todd, Architettura dei calcolatori : un approccio strutturale, 6. ed, Pearson, 2013, p. 187, ISBN 9788871929620, OCLC 928913777. URL consultadu su 2 cabudanni 2019.

- ↑ Toy, Wing e Zee, Benjamin, Computer hardware/software architecture, Prentice-Hall, 1986, p. 30, ISBN 0131635026, OCLC 12663942. URL consultadu su 10 cabudanni 2019.

- ↑ Tanenbaum, Andrew S., 1944-, Operating systems : design and implementation, 3rd ed, Pearson/Prentice Hall, 2006, ISBN 0131429388, OCLC 61859929. URL consultadu su 9 cabudanni 2019.

| Controllu de autoridade | GND (DE) 4176909-0 · LCCN (EN) sh85111346 |

|---|